### DESCRIPTION

The PT16103 is a CMOS silicon source driver IC for active matrix TFT LCD panels. After a CMOS/RSDS 6-bit RGB data is applied, this device will generate 64-gray scale for driving the TFT LCD panel source lines. It supports 480/402 channel selectable function, shift right/left selectable function, and cascade function for dot expansion.

#### **FEATURES**

- 64-gray scale source driver for active matrix TFT LCD panels

- Selectable 480/402 output channels

- Logic voltage power supply: 2.7V to 3.6V

- High voltage power supply: 7.0V to 13.5V

- Maximum RSDS operating frequency at 85 MHz

- Bi-directional shift right/left function

- COG package

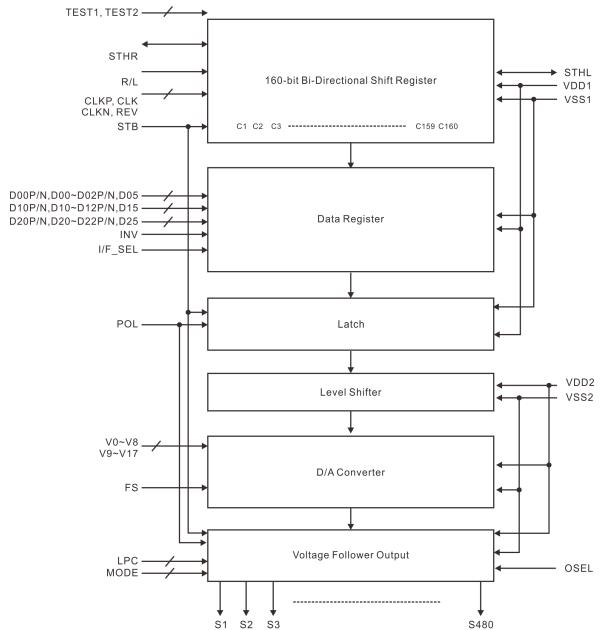

# BLOCK DIAGRAM

### **1. ORDER INFORMATION**

| Valid Part Number | Package Type | Top Code |

|-------------------|--------------|----------|

| PT16103           | COG          | -        |

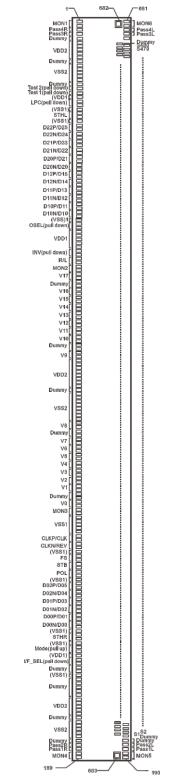

## **2. PIN CONFIGURATION**

## **3. PIN DESCRIPTION**

| Cumphed                                                              | Pin Name                                     | 1/0        | Deseriation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------|----------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol<br>S1 to S480                                                 |                                              | <b>I/O</b> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 31103400                                                             | Driver output                                |            | The D/A converted 64-qray-scale analog voltage is output.<br>A setup of this pin performs IIF input mode change of this IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| I/F_SEL                                                              | Interface select                             | I          | When I/F_SEL pin = L or open, it becomes RSDS I/F mode.<br>When I/F_SEL pin = H, it becomes CMOS I/F mode.<br>This pin is pull downed to VSS1 inside IC.<br>Cautions are required for the pin function and the electrical property of this IC to<br>change with setup of this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| D00P/N,<br>D00 to D02P/N,<br>D05<br>D10P/N,<br>D10 to D12P/N,<br>D15 | Display data                                 | l(Note)    | The function of this pin changes with setup of I/F_SEL pin.<br>When I/F_SEL pin = L or open, it becomes a display data input pin in RSDS I/F<br>mode (D00 PIN. to D02P/N, D10P/N to D12P/N, D20P/N to D22P/N).<br>Display data is inputted by the 9-bit width of the edge of double, i.e., gray-scale data<br>(6 bits) x 3dots (1 pixel).<br>When I/F_SEL pin = H, It becomes a display data input pin in CMOS I/F mode (D00<br>to D15, D10 to D15, D20 to D25).                                                                                                                                                                                                                                                                                                            |

| D20P/N,<br>D20 to D22P/N,<br>D25                                     |                                              |            | Display data is inputted by the 18-bit width of single edge, i.e, gray-scale data (6 bits) x 3 dots (1pixel).<br>D x 0: LSB, D x 5: MSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CLKP, CLK,<br>CLKN, REV                                              | Shift clock,<br>CMOS data<br>inversion (REV) | l(Note)    | The function of this pin changes with setup of I/F_SEL pin.<br>When I/F_SEL pin = L or open, it becomes a shift clock input pin by the pair of CLKP and CLKN in the RSDS I/F mode.<br>It is the shift clock input of a shift register. Display data is taken in to a data register by both the rising edge and the falling edge.<br>When I/F_SEL pin = H, it is set to the CLK (shift clock input) input pin in CMOS I/F mode, and REV (inverted/not inverted selection signal of display input data).<br>CLK takes in display data to a data register by the rising edge.<br>REV: Performs being inverted/not inverted of D00-D05, D10-D15 and D20-D25 display data.<br>REV = H: Display data is inverted inside IC.<br>REV = L: Inversion of input data is not performed. |

| INV                                                                  | RSDS data<br>inversion                       | I(Note)    | This is valid pin only at the time of I/F_SEL pin = L or Open.<br>Inverted/not inverted selection of the display input data in RSDS I/F mode are selected.<br>INV = H: Inverts data inside this IC<br>INV = L: Inversion of input data is not perform<br>Input DC signal into this pin. For more details, <b>Refer to DATA INVERSION</b><br>This pin is pull downed to VSS1 inside IC.<br>Moreover, it becomes invalid when I/F_SEL pin = H( CMOS I/F mode).<br>(As for the pull down of this pin, it exists also at the time of invalid).                                                                                                                                                                                                                                  |

| R,/L                                                                 | Shift direction control                      | I          | These refer to the start pulse input/output pins when driver ICs is connected in cascade. The shift directions of the shift registers are as follows.<br>R,/L = H: STHR input, S1 $\rightarrow$ S480, STHL output<br>R,/L = L: STHL input, S480 $\rightarrow$ S1, STHR output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| STHR(CMOS)                                                           | Right shift start<br>pulse                   | I/O        | R,/L= H: Becomes the start pulse input pin<br>R,IL = L: Becomes the start pules output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| STHL(CMOS)                                                           | Left shift start<br>pulse                    | I/O        | R,/L = H: Becomes the start pules output pin<br>R,/L= L: Becomes the start pulse input pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| STB(CMOS)                                                            | Latch                                        | I          | The contents of the data register are transferred to the latch circuit at rising edges.<br>At the falling edge of STB, the gray scale voltage is supplied to the driver.<br>It is necessary to input before start pulse input<br>When there is no STB signal input and a start pulse is inputted continuously,<br>loading the data based on a start pulse not performed.                                                                                                                                                                                                                                                                                                                                                                                                    |

| POL(CMOS)                                                            | Polarity select                              | I          | This is the output polarity selection input pin of a driver output.<br>POL = H: S2n-1 output uses V0 to V8 as a reference power supply.<br>The S2n output used V9 to V17 as the reference supply<br>POL = L: S2n-1 output uses V9 to V17 as a reference power supply.<br>The S2n output used V0 to V8 as the reference supply<br>S2n-1 indicates odd output and S2n indicates the even output.                                                                                                                                                                                                                                                                                                                                                                              |

PT16103

| Symbol                          | Pin Name                         | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------|----------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE(CMOS)                      | Output reset                     | I   | The pin controls output reset function.<br>MODE: H or OPEN: With output reset(during the STB=H period)<br>MODE: L: No output reset<br>This pin is pulled up to power supply VDD1 inside IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| LPC(CMOS)                       | Low power<br>control             | I   | LPC1     Driver Ability(reference ratio)       L or open     Large(100%)       H     Small(67%)   This pin is pulled down to power supply VSS1 inside IC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| OSEL(CMOS)                      | Output selection                 | I   | Output channel numbers select pin.<br>OSEL= L or Open: 480ch output<br>OSEL = H: 402ch output (S205 to S282: Hi-Z)<br>This pin is pulled down to power supply VSS1 inside IC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| V0 to V8,<br>V9 to V17          | <i>r</i> -corrected power supply | I   | Input the $\gamma$ -corrected power supply from outside by using operational amplifier.<br>V <sub>0</sub> , V <sub>8</sub> , V <sub>9</sub> , and V <sub>17</sub> input pin are not connected to ladder resistance.<br>V <sub>1</sub> , V <sub>7</sub> , V <sub>10</sub> , and V <sub>16</sub> input pin, the voltage follow circuit is attached to the inside of IC.<br>V <sub>2</sub> to V <sub>6</sub> , V <sub>10</sub> , and V <sub>11</sub> to V <sub>15</sub> input pin are connected to ladder resistance directly.<br>Make sure to maintain the following relationships. During the gray scale voltage<br>output, be sure to keep the gray scale level power supply at a constant level.<br>VDD2 - 0.1V $\ge$ V0> V1 > V2> V3 > V4 > V5 > V6 >V7 > V8 $\ge$ 0.5VDD2<br>0.5 VDD 2 $\ge$ V9 > V10 > V11 > V12 > V13 > V14 > V15 > V16 >V17 $\ge$ VSS2 + 0.1V |

| FS                              | Frame signal<br>input            | I   | The offset cancellation start signal of the voltage follower circuit with which the inside of IC of gamma corrected power supply parts V1, V7 and V10 and V16 input pin is equipped is inputted. The input if one pulse is required for easy frame. Moreover, it is necessary to make in agreement the number of times of STB inputted in each frame. Refer to <b>SWITCHING CHARACTERISTIC</b> about timing etc.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VDD1                            | Logic power<br>supply            | -   | 2.7 to 3.6 V(Connect all pins)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| (VDD1)                          | Pull for pull up                 | -   | This pin is used when carrying out the pull-up of the adjoining functional setting pin. Leave it open at the time of intact.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VDD2                            | Driver power<br>supply           | -   | 7.0 to 13.5V(Connect all pins)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VSS1                            | Logic ground                     | -   | Grounding(Connect all pins)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| (VSS1)                          | Pull for pull up                 | -   | This pin is used when carrying out the pull-down of the adjoining functional setting pin.<br>Leave it open at the time of intact.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VSS2                            | Driver ground                    | -   | Grounding(Connect all pins)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TEST1, TETS 2<br>(CMOS)         | Test pin                         | I   | TEST 1/2 = L or Open: Normal operation(Be sure to use it in the normal mode when this IC use)<br>TEST 1/2 = H: Test mode<br>This pin is pulled down to VSS1 inside IC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MON1 to MON6                    | Monitor pin                      | -   | MONn(n=1 to 6) is connected between common in numbers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PASSnR,<br>PASSnL<br>(n=1 to 4) | Pass pin                         | -   | Wiring connection if between PASSnR and PASSnL (n=1 to 4) is made inside IC between each n number in agreement (Example: PASSnR and PASSnL are connected).<br>And this pin is used for simple evaluations, such as contact resistance measurement of ACF. Therefore, the power supply relation and control signal which are used in LCD panel operation are not connectable. When this pin is unnecessary, leave this pin open.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Note: A pin function changes by setup of I/F\_SEL pin.

#### **IMPORTANT NOTICE**

Princeton Technology Corporation (PTC) reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and to discontinue any product without notice at any time. PTC cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a PTC product. No circuit patent licenses are implied.

Princeton Technology Corp. 2F, 233-1, Baociao Road, Sindian Dist., New Taipei City 23145, Taiwan Tel: 886-2-66296288 Fax: 886-2-29174598 http://www.princeton.com.tw