#### DESCRIPTION

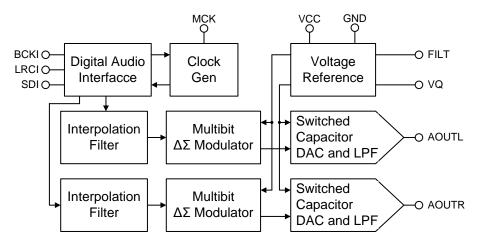

The PT3344 is a stereo audio digital to analog converter (DAC), the chip includes interpolation filter, fourth-order multi-bit delta-sigma modulator, and analog output signal is filtering by on-chip switched-capacitor low-pass filter. The digital input interface compliant to industrial standard  $I^2S$  format exclusively.

PT3344 support the audio sampling rates from 8KHz up to 200KHz, and internal timing circuit will automatic detects the clock ratio between the sample rate clock (LRCI) and system master clock (MCK) and auto-select the proper clock for system processing.

## **APPLICATIONS**

- Set top box

- Home theater

- TV or PC display audio decoding

- Projector

#### **FEATURES**

- Single +3.3V or +5V Power Supply

- Support Sample Rates : 8 ~ 192KHz

- Support 24-bit Audio Data Conversion

- Support I<sup>2</sup>S format exclusively

- 102 dB Dynamic Range

- -85 dB THD+N

- Multi-bit Delta-Sigma Modulator

- Auto-Detect MCK/LRCI clock Ratio

- Low Clock-Jitter Sensitivity

- On-chip Low-pass Filter for Line-Level Outputs

- 10-pin MSOP Package

## BLOCK DIAGRAM

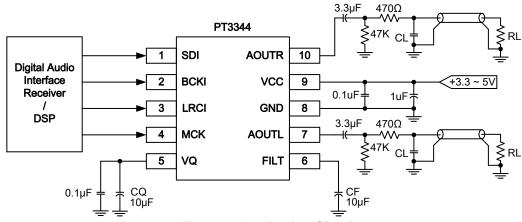

## **APPLICATION CIRCUIT**

#### Figure 1, Application Circuit

| Part No. | Recommended Value | Description                                                                                                      |

|----------|-------------------|------------------------------------------------------------------------------------------------------------------|

| CF       | 10µF              | Bypass capacitor for internal voltage reference                                                                  |

| CQ       | 10µF // 0.1µF     | Output soft ramps-up time control, applies a $10\mu F$ cap for 450ms delay, and 3.3 $\mu F$ for 280ms delay.     |

| CL       | 3300pF            | External low-pass filter in-cooperates with a 470 $\Omega$ resistor.                                             |

| RL       | >10KΩ             | Output AC-loaded resistance, should not lower than recommend value to achieve specified full-scale output level. |

Table 1, Application circuit parts recommendation

### **ORDER INFORMATION**

| Valid Part Number | Package Type | Top Code |  |

|-------------------|--------------|----------|--|

| PT3344            | 10 Pin, MSOP | PT3344   |  |

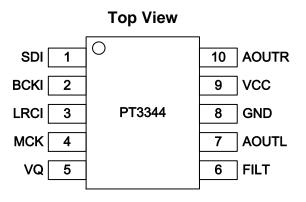

### **PIN CONFIGURATION**

PT3344

#### **PIN DESCRIPTION**

| Pin Name | I/O   | Description                                                             |  |  |

|----------|-------|-------------------------------------------------------------------------|--|--|

| SDI      | I     | Input pin for two's complement serial audio data.                       |  |  |

| BCKI     | I     | Input pin for serial clock input.                                       |  |  |

| LRCI     | I     | Input pin for sample rate clock input.                                  |  |  |

| MCK      | I     | Input pin for chip mater clock input                                    |  |  |

| VQ       | Power | Internal output bias voltage reference bypassing                        |  |  |

| FILT     | 0     | Internal reference voltage bypassing for delta-sigma modulator circuits |  |  |

| AOUTL    | 0     | The left channel analog line level output                               |  |  |

| GND      | Power | Chip ground                                                             |  |  |

| VCC      | Power | Positive power input for the analog and digital sections                |  |  |

| AOUTR    | 0     | The right channel analog line level output.                             |  |  |

# FUNCTION DESCRIPTION

### MASTER CLOCK AND I<sup>2</sup>S DATABUS

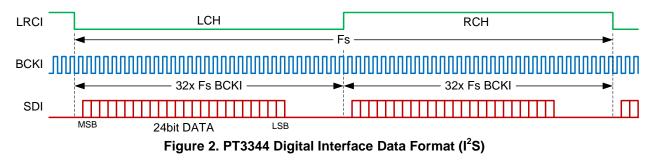

The MCK and LRCI clock must be an integer ratio, as shown in Table 1. The LRCI frequency is equal to audio sample rate (Fs), the MCK-to-LRCI frequency ratio detected automatically during the initialization procedure by counting the number of MCK transitions during a single LRCI period, next the internal dividers determinate the relatives speed mode of modulator and digital interpolation filter. The Table 2 shows several standard audio sample rates and correspond MCK and LRCI frequencies. Please note the MCK, LRCI and BCKI clocks must be synchronous and edge alignment.

| LRCI                                  |         | MCK(MHz) |         | Recommendation                                                          |  |  |  |

|---------------------------------------|---------|----------|---------|-------------------------------------------------------------------------|--|--|--|

| (KHz)                                 | 128x    | 256x     | 512x    |                                                                         |  |  |  |

| 32                                    | -       | 8.192    | -       | If Fs≤96 KHz, choose 256x Fs clock as MCK.                              |  |  |  |

| 44.1                                  | -       | 11.2896  | 22.5792 | If Fs>96 KHz, choose 128x Fs clock as MCK.                              |  |  |  |

| 48                                    | -       | 12.288   | 24.576  | The maximum MCK frequency should not exceeds 30MHz.                     |  |  |  |

| 88.2                                  | 11.2896 | 22.5792  | -       | <ul> <li>QSM (Quarter Speed Mode), HSM (Half Speed Mode) and</li> </ul> |  |  |  |

| 96                                    | 12.288  | 24.576   | -       | FSM (Full Speed Mode) is uses to determinate interpolation              |  |  |  |

| 176.4                                 | 22.5792 | -        | -       | filter clock and coefficients.                                          |  |  |  |

| 192                                   | 24.576  | -        | -       |                                                                         |  |  |  |

| Mode                                  | QSM     | HSM      | FSM     |                                                                         |  |  |  |

| Table 2, Master clock selection table |         |          |         |                                                                         |  |  |  |

The serial bit clock (BCKI) is the shift clock of the SDI input data. The rising edge of BCKI must align to the center portion of SDI data hold times. The BCKI/LRCI clock ratio is fixed in 64x Fs for proper 24bit audio data decoding. In the Figures 2 shows  $I^2S$  data formats and clock relationship.

#### IMPORTANT NOTICE

Princeton Technology Corporation (PTC) reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and to discontinue any product without notice at any time. PTC cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a PTC product. No circuit patent licenses are implied.

Princeton Technology Corp. 2F, 233-1, Baociao Road, Sindian Dist., New Taipei City 23145, Taiwan Tel : 886-2-66296288 Fax: 886-2-29174598 http://www.princeton.com.tw