#### **DESCRIPTION**

PT2509 is a full-bridge driver with build-in driving pattern for the swing head motor application.

It integrates the over temperature protection, short-circuit protection, and under voltage protection. With one EN control pin, the PT2509 will deliver 50Hz PWM waveform to drive the AC synchronous motor. Besides the 50Hz pattern, a clock signal can also feed to EN pin to operate with required frequency. PT2509 with package in SOP8.

## **FEATURES**

- Full-bridge driver with fixed pattern for AC synchronous motor

- Short Circuit Protection (SCP)

- Over Temperature Protection (OTP)

- Under Voltage Lock-Out protection (UVLO)

- Sinewave or trapezoid-like driving waveform

- 40Hz to 100Hz adjustable driving frequency

## **APPLICATIONS**

Fan with swing head motor

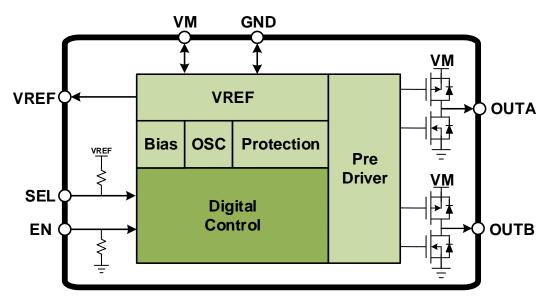

### **BLOCK DIAGRAM**

## **ORDER INFORMATION**

| Part Number | Package    | Top Logo |

|-------------|------------|----------|

| PT2509-S    | 8-PIN, SOP | PT2509-S |

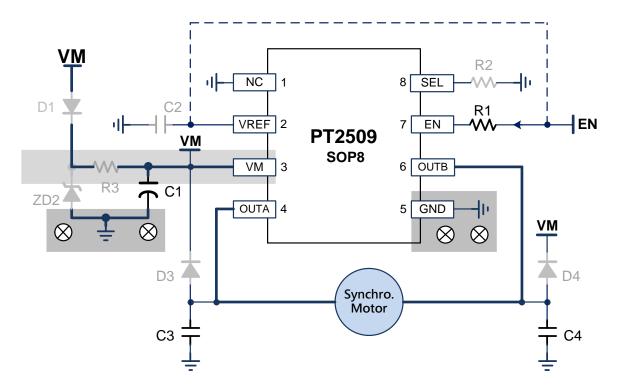

# **APPLICATION BLOCK DIAGRAM**

| Part  | Value   | Unit | Description                                                                                               |  |

|-------|---------|------|-----------------------------------------------------------------------------------------------------------|--|

| R1    | 1K      | Ω    | Protection resistor for EN input                                                                          |  |

| R2    | 1K      | Ω    | Setting resistor for SEL input(option)                                                                    |  |

| R3    | 0~1     | Ω    | Filter resistor over the VM input(option) *its selection need care about power rating and heat generation |  |

| C1    | 10u/50V | F    | Filter capacitor over VM                                                                                  |  |

| C2    | NC~100p | F    | Filter capacitor for VREF(option) *<100pF will not influence to circuit response                          |  |

| C3/C4 | 10n/50V | F    | Surge voltage suppressing capacitor over motor terminal                                                   |  |

| D1    | >50V/2A | V    | Reverse supply voltage protection(option)                                                                 |  |

| ZD2   | 27V/1A  | V    | Surge voltage suppressing over VM(option)                                                                 |  |

| D3/D4 | >50V/1A | V    | Surge voltage suppressing diode over motor terminal(option). *1N4148                                      |  |

V 1.0E 2 Apr 2023

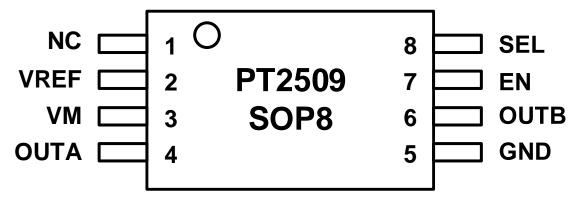

## **PIN ASSIGNMENT**

## **PIN DESCRIPTION**

| Pin Name    | I/O/P | Description                                                                                                                                                                                                                                                                                                         | Pin No. |

|-------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Pili Naille | 1/0/P | Description                                                                                                                                                                                                                                                                                                         | 8 Pin   |

| NC          |       | No connection(or connect to GND)                                                                                                                                                                                                                                                                                    | 1       |

| VREF        | Р     | +5V reference voltage for internal use                                                                                                                                                                                                                                                                              | 2       |

| VM          | Р     | Power supply                                                                                                                                                                                                                                                                                                        | 3       |

| OUTA        | 0     | Full-bridge driver output A                                                                                                                                                                                                                                                                                         | 4       |

| GND         | Р     | Signal ground                                                                                                                                                                                                                                                                                                       | 5       |

| OUTB        | 0     | Full-bridge driver output B                                                                                                                                                                                                                                                                                         | 6       |

| EN          | I     | It can apply with DC or clock input DC input: 0V to disable, 5V to enable and default driving frequency is 50Hz Clock input: 40Hz to 100Hz square wave input to set the driving frequency EN is internal pull-down to GND via $100 \mathrm{K}\Omega$ and recommend in series an $1 \mathrm{K}\Omega$ resistor to it | 7       |

| SEL         | I     | Driving mode selection 5V to sinewave(default) 0V to trapezoid wave SEL is internal pull-up to VREF via 100ΚΩ                                                                                                                                                                                                       | 8       |

# PIN EQUIVALENT CIRCUIT

| VM/VREF | OUTA/OUTB | EN | SEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|-----------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VM<br>  | OUTA/OUTB | EN | VREF<br>\$100ΚΩ<br>SEL WATER AND THE SEL T |

#### **IMPORTANT NOTICE**

Princeton Technology Corporation (PTC) reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and to discontinue any product without notice at any time. PTC cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a PTC product. No circuit patent licenses are implied.

Princeton Technology Corp. 2F, 233-1, Baociao Road, Sindian Dist., New Taipei City 23145, Taiwan Tel: 886-2-66296288

Fax: 886-2-29174598 http://www.princeton.com.tw