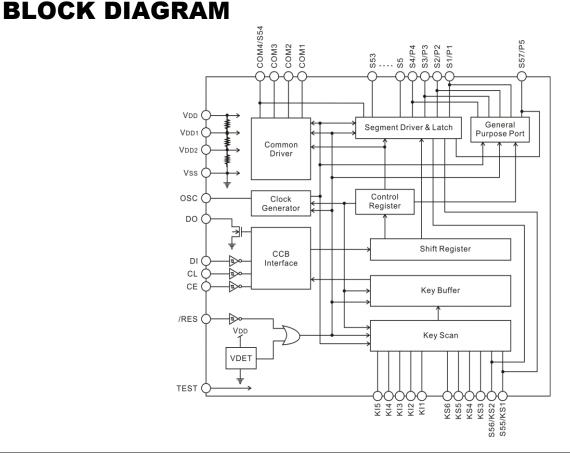

#### PT16589 1/4 and 1/3-Duty LCD Display Driver with Key Input Function

# DESCRIPTION

The PT16589 is 1/4 duty and 1/3 duty LCD display driver that can directly drive up to 224 segments and can control up to 5 general-purpose output ports. This product also incorporates a key scan circuit that accepts input from up to 30 keys to reduce printed circuit board wiring.

# APPLICATION

• Electronic Equipment with LCD Display

# **FEATURES**

- Key input function for up to 30 keys (A key scan is performed only when a key is pressed.)

- 1/4 duty 1/3 bias and 1/3 duty 1/3 bias drive schemes can be controlled from serial data.

- Capable of driving up to 224 segments using 1/4 duty and up to 171 segments using 1/3 duty.

- Switching between key scan output and segment output can be controlled from serial data.

- The key scan operation enabled/disabled state can be controlled from serial data.

- Switching between segment output port and generalpurpose output port can be controlled from serial data.

- Switching between general-purpose output port, clock output port, and segment output port can be controlled from serial data. (Up to 5 general-purpose output ports and up to one clock output port)

- Serial data I/O supports CCB format communication with the system controller. (Support 3.3V and 5V operation)

- Sleep mode and all segments off functions that are controlled from serial data.

- The frame frequency of the common and segment output waveforms can be controlled from serial data.

- Switching between RC oscillator operating mode and external clock operating mode can be controlled from serial data.

- Direct display of display data without the use of a decoder provides high generality.

- Provision of an on-chip voltage-detection type reset circuit prevents incorrect displays.

- /RES pin provided for forcibly initializing the IC internal circuits.

#### Tel: 886-2-66296288 • Fax: 886-2-29174598 • http://www.princeton.com.tw • 2F, No. 233-1, Baociao Rd., Sindian Dist., New Taipei City 23145, Taiwan

## CONTENTS

| 1. APPLICATION CIRCUITS                                                    | 3 |

|----------------------------------------------------------------------------|---|

| 1.1 1/4 DUTY, 1/3 BIAS (FOR USE WITH NORMAL PANELS)                        | 3 |

| 1.2 1/4 DUTY, 1/3 BIAS (FOR USE WITH LARGE PANELS)                         | 4 |

| 1.3 1/3 DUTY, 1/3 BIAS (FOR USE WITH NORMAL PANELS)                        | 5 |

| 1.4 1/3 DUTY, 1/3BIAS (FOR USE WITH LARGE PANELS)                          | 6 |

| 2. ORDER INFORMATION                                                       | 7 |

| 3. PIN CONFIGURATION                                                       |   |

| 4. PIN DESCRIPTION                                                         |   |

| 5. FUNCTION DESCRIPTION                                                    |   |

| 5.1 SERIAL DATA INPUT                                                      |   |

| 5.2 CONTROL DATA FUNCTIONS                                                 |   |

| 5.3 DISPLAY DATA AND OUTPUT PIN CORRESPONDENCE                             |   |

| 5.4 SERIAL DATA OUTPUT                                                     |   |

| 5.5 OUTPUT DATA                                                            |   |

| 5.6 SLEEP MODE FUNCTIONS                                                   |   |

| 5.7 KEY SCAN OPERATION FUNCTIONS                                           |   |

| 5.8 MULTIPLE KEY PRESSES                                                   |   |

| 5.9 1/4 DUTY, 1/3 BIAS DRIVE TECHNIQUE                                     |   |

| 5.10 1/3 DUTY, 1/3 BIAS DRIVE TECHNIQUE                                    |   |

| 5.11 CLOCK SIGNAL OUTPUT WAVEFORM                                          |   |

| 5.12 VOLTAGE DETECTION TYPE RESET CIRCUIT (VDET)                           |   |

| 5.13 SYSTEM RESET                                                          |   |

| 5.14 NOTES ON THE OSC PIN PERIPHERAL CIRCUIT                               |   |

| 5.15 NOTES ON TRANSFERRING DISPLAY DATA FROM THE CONTROLLER                | - |

| 5.16 NOTES ON THE CONTROLLER KEY DATA READ TECHNIQUES                      |   |

| 5.17 ABOUT DATA COMMUNICATION METHOD WITH THE CONTROLLER                   |   |

| 5.18 DATA COMMUNICATION FLOWCHART OF 4 LINE TYPE OR 3 LINE TYPE CCB FORMAT |   |

| 5.19 TIMING CHART OF 4 LINE TYPE AND 3 LINE TYPE CCB FORMAT                |   |

| 6. ABSOLUTE MAXIMUM RATINGS                                                |   |

| 7. ALLOWABLE OPERATING RANGES                                              |   |

| 8. ELECTRICAL CHARACTERISTICS.                                             |   |

| 9. PACKAGE INFORMATION                                                     |   |

| IMPORTANT NOTICE                                                           |   |

# **1. APPLICATION CIRCUITS**

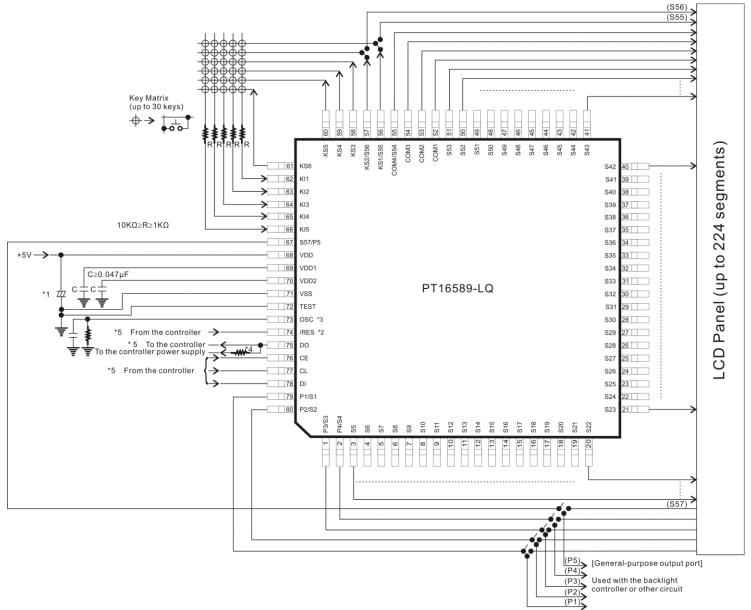

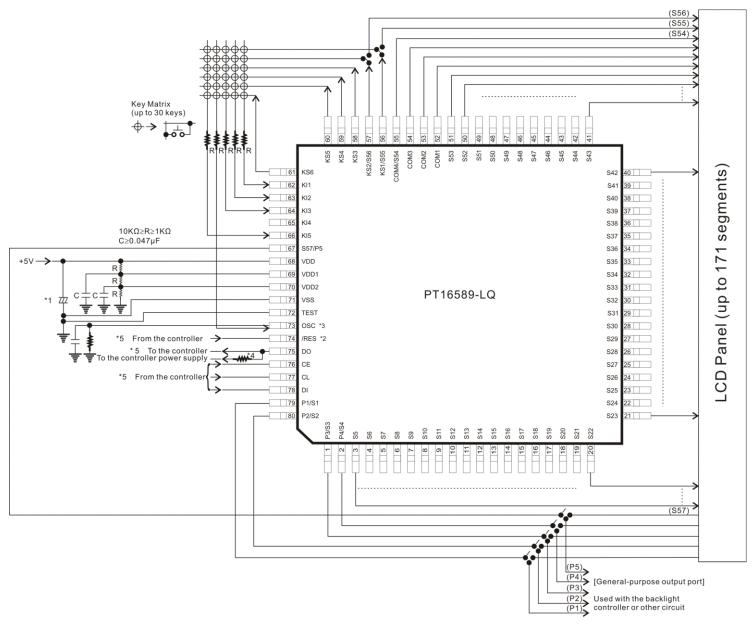

## 1.1 1/4 DUTY, 1/3 BIAS (FOR USE WITH NORMAL PANELS)

- Add a capacitor to the power supply line so that the power supply voltage V<sub>DD</sub> rise time when power is applied and the power supply voltage V<sub>DD</sub> fall time when power drops are both at least 1ms, as the PT16589 is reset by the V<sub>DET</sub>.

- 2. If the /RES pin is not used for system reset, it must be connected to the power supply  $V_{DD}$ .

- 3. When RC oscillator operating mode is used, the external resistor ROSC and the external capacitor COSC must be connected between the OSC pin and GND, and when external clock operating mode is selected the current protection resistor Rg (4.7 to 47KΩ) must be connected between the OSC pin and the external clock output pin (external oscillator). (See the section on the OSC pin peripheral circuit.)

- 4. The DO pin, being an open-drain output, requires a pull-up resistor. Select a resistance (between 1 to 10KΩ) appropriate for the capacitance of the external wiring so that signal waveforms are not degraded.

- 5. The pins to be connected to the controller (CE, CL, DI, DO, /RES) can handle 3.3V or 5V.

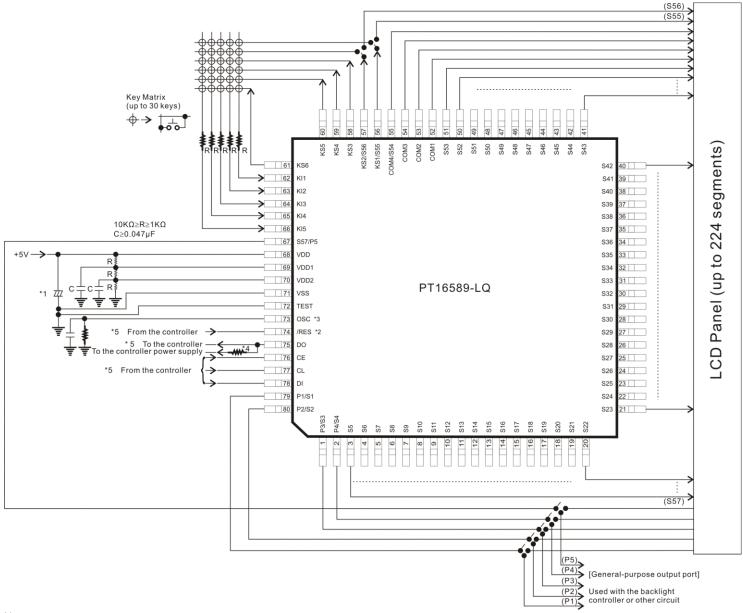

## 1.2 1/4 DUTY, 1/3 BIAS (FOR USE WITH LARGE PANELS)

- Add a capacitor to the power supply line so that the power supply voltage V<sub>DD</sub> rise time when power is applied and the power supply voltage V<sub>DD</sub> fall time when power drops are both at least 1ms, as the PT16589 is reset by the V<sub>DET</sub>.

- 2. If the /RES pin is not used for system reset, it must be connected to the power supply  $V_{DD}$ .

- 3. When RC oscillator operating mode is used, the external resistor ROSC and the external capacitor COSC must be connected between the OSC pin and GND, and when external clock operating mode is selected the current protection resistor Rg (4.7 to 47KΩ) must be connected between the OSC pin and the external clock output pin (external oscillator). (See the section on the OSC pin peripheral circuit.)

- 4. The DO pin, being an open-drain output, requires a pull-up resistor. Select a resistance (between 1 to 10KΩ) appropriate for the capacitance of the external wiring so that signal waveforms are not degraded.

- 5. The pins to be connected to the controller (CE, CL, DI, DO, /RES) can handle 3.3V or 5V.

## 1.3 1/3 DUTY, 1/3 BIAS (FOR USE WITH NORMAL PANELS)

- Add a capacitor to the power supply line so that the power supply voltage V<sub>DD</sub> rise time when power is applied and the power supply voltage V<sub>DD</sub> fall time when power drops are both at least 1ms, as the PT16589 is reset by the V<sub>DET</sub>.

- 2. If the /RES pin is not used for system reset, it must be connected to the power supply  $V_{DD}$ .

- 3. When RC oscillator operating mode is used, the external resistor ROSC and the external capacitor COSC must be connected between the OSC pin and GND, and when external clock operating mode is selected the current protection resistor Rg (4.7 to 47KΩ) must be connected between the OSC pin and the external clock output pin (external oscillator). (See the section on the OSC pin peripheral circuit.)

- 4. The DO pin, being an open-drain output, requires a pull-up resistor. Select a resistance (between 1 to 10KΩ) appropriate for the capacitance of the external wiring so that signal waveforms are not degraded.

- 5. The pins to be connected to the controller (CE, CL, DI, DO, /RES) can handle 3.3V or 5V.

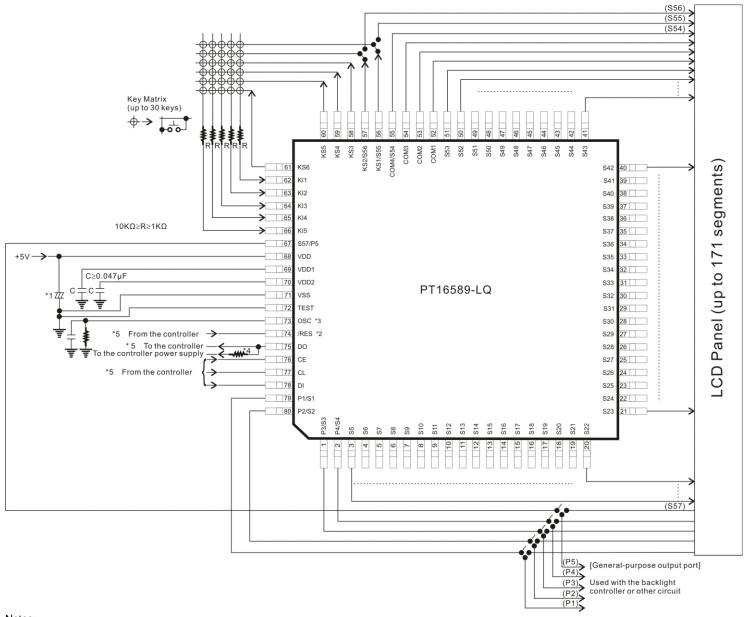

## 1.4 1/3 DUTY, 1/3BIAS (FOR USE WITH LARGE PANELS)

- 1. Add a capacitor to the power supply line so that the power supply voltage VDD rise time when power is applied and the power supply voltage VDD fall time when power drops are both at least 1ms, as the PT16589 is reset by the VDET.

- 2. If the /RES pin is not used for system reset, it must be connected to the power supply VDD.

- 3. When RC oscillator operating mode is used, the external resistor ROSC and the external capacitor COSC must be connected between the OSC pin and GND, and when external clock operating mode is selected the current protection resistor Rg (4.7 to 47KΩ) must be connected between the OSC pin and the external clock output pin (external oscillator). (See the section on the OSC pin peripheral circuit.)

- The DO pin, being an open-drain output, requires a pull-up resistor. Select a resistance (between 1 to 10KΩ) appropriate for the capacitance of the external wiring so that signal waveforms are not degraded.

- 5. The pins to be connected to the controller (CE, CL, DI, DO, /RES) can handle 3.3V or 5V.

# **2. ORDER INFORMATION**

|                    |       |       |               | -       | -       |           |      |      | _    |          | _                    |            |     | -   |     |     | _   | -    | -           |     |            |

|--------------------|-------|-------|---------------|---------|---------|-----------|------|------|------|----------|----------------------|------------|-----|-----|-----|-----|-----|------|-------------|-----|------------|

|                    | Va    |       | art 1<br>6589 |         |         |           |      |      |      |          | j <b>e Ty</b><br>LQI |            |     |     |     |     |     | p Co | ode<br>9-LQ | )   |            |

|                    |       |       | 000.          |         |         |           |      |      | 00   | <u> </u> |                      |            |     |     |     |     |     | 000  |             |     |            |

| IN C               | ON    | IF    | IG            | U       | R/      | <b>\T</b> | 10   | N    |      |          |                      |            |     |     |     |     |     |      |             |     |            |

|                    |       |       |               |         |         |           |      |      |      |          |                      |            |     |     |     |     |     |      |             |     |            |

|                    | 60    | 59    | 58            | 57      | 56      | 55        | 54   | 53   | 52   | 51       | 50                   | 49         | 48  | 47  | 46  | 45  | 44  | 43   | 42          | 41  |            |

|                    | KS5   | KS4   | KS3           | 556     | 355     | 554       | COM3 | COM2 | COM1 | S53      | S52                  | S51        | S50 | S49 | S48 | S47 | S46 | S45  | S44         | S43 |            |

| 61 KS6             | x     | x     | x             | KS2/S56 | KS1/S55 | COM4/S54  | 00   | 00   | 00   | 0)       | 0)                   | 0,         | 0)  | 0)  | 0)  | 0)  | 0)  | 0)   | 0)          | 0)  | S42        |

| 52 KI1             |       |       |               | -       | -       | ö         |      |      |      |          |                      |            |     |     |     |     |     |      |             |     | S41        |

| 63 KI2             |       |       |               |         |         |           |      |      |      |          |                      |            |     |     |     |     |     |      |             |     | S40        |

| 64 KI3             |       |       |               |         |         |           |      |      |      |          |                      |            |     |     |     |     |     |      |             |     | S39        |

| 65 KI4             |       |       |               |         |         |           |      |      |      |          |                      |            |     |     |     |     |     |      |             |     | S38        |

| 66 KI5             |       |       |               |         |         |           |      |      |      |          |                      |            |     |     |     |     |     |      |             |     | S37        |

| 67 S57/P           | 5     |       |               |         |         |           |      |      |      |          |                      |            |     |     |     |     |     |      |             |     | S36        |

|                    |       |       |               |         |         |           |      |      |      |          |                      |            |     |     |     |     |     |      |             |     | S35        |

| 69 VDD1<br>70 VDD2 |       |       |               |         |         |           |      |      |      |          |                      |            |     |     |     |     |     |      |             |     | S34<br>S33 |

| 71 VSS             |       |       |               |         |         |           |      | Ρ    | ΥT1  | 65       | 589                  | )-L        | Q   |     |     |     |     |      |             |     | S33        |

| 72 TEST            |       |       |               |         |         |           |      |      |      |          |                      |            |     |     |     |     |     |      |             |     | S31        |

| 73 OSC             |       |       |               |         |         |           |      |      |      |          |                      |            |     |     |     |     |     |      |             |     | S30        |

| 74 /RES            |       |       |               |         |         |           |      |      |      |          |                      |            |     |     |     |     |     |      |             |     | S29        |

| 75 DO              |       |       |               |         |         |           |      |      |      |          |                      |            |     |     |     |     |     |      |             |     | S28        |

| 6 CE               |       |       |               |         |         |           |      |      |      |          |                      |            |     |     |     |     |     |      |             |     | S27        |

| 7 CL               |       |       |               |         |         |           |      |      |      |          |                      |            |     |     |     |     |     |      |             |     | S26        |

| 78 DI              |       |       |               |         |         |           |      |      |      |          |                      |            |     |     |     |     |     |      |             |     | S25        |

| 9 P1/S1            |       |       |               |         |         |           |      |      |      |          |                      |            |     |     |     |     |     |      |             |     | S24        |

| 80 P2/S2           |       | S4    |               |         |         |           |      | ~    |      | ~        | ~                    | <b>-</b> + | 10  | (0  | r   | ~   | ¢   | 0    | _           |     | S23        |

|                    | P3/S3 | P4/S4 | S5            | S6      | S7      | S8        | S9   | S10  | S11  | S12      | S13                  | S14        | S15 | S16 | S17 | S18 | S19 | S20  | S21         | S22 |            |

| -                  | -     | 2     | З             | 4       | 5       | 9         | 7    | 8    | 6    | 10       | 11                   | 12         | 13  | 14  | 15  | 16  | 17  | 18   | 19          | 20  |            |

|                    |       |       |               |         |         |           |      |      |      |          |                      |            |     |     |     |     |     |      |             |     |            |

# **4.PIN DESCRIPTION**

| Pin Name I/O Active              |     | Active | Handling when<br>unused | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                     |  |  |  |  |

|----------------------------------|-----|--------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--|--|--|--|

| S1/P1 to S4/P4<br>S5 to S53      | 0   | -      | OPEN                    | Segment outputs for displaying the display data transferred by serial data input. The S1/P1 to S4/P4 pins can be used as general-purpose output ports under serial data control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 79,80,1,<br>3 to 51 |  |  |  |  |

| COM1 to COM3<br>COM4/S54         | 0   | -      | OPEN                    | Common driver outputs. The frame frequency is fo[Hz].<br>The COM4/S54 pin can be used as a segment output in 1/3 duty.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 52 to 54<br>55      |  |  |  |  |

| KS1/S55<br>KS2/S56<br>KS3 to KS6 | 0   | -      | OPEN                    | Key scan outputs. Although normal key scan timing lines require<br>diodes to be inserted in the timing lines to prevent shorts, since<br>these outputs are unbalanced CMOS transistor outputs, these<br>outputs will not be damaged by shorting when these outputs are<br>used to form a key matrix. The KS1/S55 to KS2/S56 pins can be<br>used as segment outputs when so specified by the control data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 56<br>57<br>58 to 6 |  |  |  |  |

| KI1 to KI5                       | I.  | Н      | GND                     | Key scan inputs. These pins have built-in pull-down resistors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 62 to 6             |  |  |  |  |

| S57/P5                           | 0   | -      | OPEN                    | Logic block power supply connection. Provide a voltage of between 2.7 and 6.0V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 67                  |  |  |  |  |

| V <sub>DD</sub>                  | -   | -      | -                       | Power supply connections. Provide a voltage of between 4.5 to 6.0V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 68                  |  |  |  |  |

| Vdd1                             | Ι   | -      | OPEN                    | Used for applying the LCD drive $2/3$ bias voltage externally. Must be connected to V <sub>LCD2</sub> when a $1/2$ bias drive scheme is used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 69                  |  |  |  |  |

| Vdd2                             | Ι   | -      | OPEN                    | Used for applying the LCD drive 1/3 bias voltage externally. Must be connected to $V_{LCD1}$ when a 1/2 bias drive scheme is used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 70                  |  |  |  |  |

| Vss                              | -   | -      | -                       | Power supply connection. Connect to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 71                  |  |  |  |  |

| TEST                             | Ι   | -      | -                       | This pin must be connected to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 72                  |  |  |  |  |

| OSC                              | I/O | -      | V <sub>DD</sub>         | The OSC pin can be used to form an oscillator circuit with an external resistor and an external capacitor. If external clock mode is selected with the control data, this pin is used to input an external clock signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 73                  |  |  |  |  |

| /RES                             | I   | L      | V <sub>DD</sub>         | Reset signal input<br>./RES=Low ·····Display off<br>- S1/P1 to S4/P4, KS1/S55, KS2/S56=Low<br>(These pins are forcibly set to the segment output port function<br>and fixed at the low level.)<br>- S5 to S53=Low<br>- COM1 to COM3=Low<br>- COM4/S54=Low<br>(This pin is forcibly set to the common output function and fixed at<br>the low level.)<br>- S57/P5=Low<br>(This pin is forcibly set to the general-purpose output port function<br>and fixed at the low level.)<br>- KS3 to KS6=Low<br>- Key scanning disabled<br>- All the key data is reset to low.<br>- OSC="Z"(High impedance)<br>- RC oscillation stopped<br>- Inhibits external clock input<br>./RES=High ···· Display on<br>- General-purpose output port state setting is enabled<br>- Key scanning is enabled.<br>- RC oscillation enabled (RC oscillator operating mode)<br>- Enables external clock input (external clock operating mode)<br>However, serial data can be transferred when the RES pin is low | 74                  |  |  |  |  |

| DO                               | 0   | _      | OPEN                    | Serial data interface connections to the controller. Note that DO,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 75                  |  |  |  |  |

| 50                               |     | H      |                         | being an open-drain output, requires a pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 76                  |  |  |  |  |

| CF                               |     |        |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                     |  |  |  |  |

| CE                               |     |        | GND                     | DO: Output data<br>CE: Chip enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 77                  |  |  |  |  |

### **IMPORTANT NOTICE**

Princeton Technology Corporation (PTC) reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and to discontinue any product without notice at any time.

PTC cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a PTC product. No circuit patent licenses are implied.

Princeton Technology Corp. 2F, 233-1, Baociao Road, Sindian Dist., New Taipei City 23145, Taiwan Tel: 886-2-66296288 Fax: 886-2-29174598 http://www.princeton.com.tw